Xilinx Serial To Parallel Shift Register

Xilinx Glossary

EE Times connects the global electronics community through news, analysis, education, and peer-to-peer discussion around technology, business, products and design.

- Lab Workbook Modeling Registers and Counters www.xilinx.com/university Nexys4 6-1 xup xilinx.com copyright 2013 Xilinx Modeling Registers and Counters.

- Definitions for commonly used terms on Xilinx.com and in Xilinx documentation. Browse the glossary, or choose one of the following terms.

Spartan-6 Family Overview DS160 v2.0 October 25, 2011 www.xilinx.com Product Specification 8 Low-Power Gigabit Transceiver Ultra-fast data transmission between.

Verilog TUTORIAL for beginners We had earlier published a Verilog tutorial that made use of the Xilinx ISE Simulator. We had received very favorable response for the.

Spartan-3E FPGA Family: Introduction and Ordering Information DS312 v4.1 July 19, 2013 www.xilinx.com Product Specification 6 Ordering Information.

The magic of the shift register. The shift register is an easy-to-manage component. We will dedicate a series of articles illustrating applications giving us the.

P1dB

One-decibel compression point

PA

Power Amplifier

PACE

Pinout Area Constraints Editor. A GUI tool that defines legal pin assignments and creates properly sized area constraints.

package

The physical packaging of a chip, for example, PG84, VQ100, and PC48.

Package Designator

Materials listed are package related. To relate information to a specific device part number, refer to the package designator portion of the part number. For example: XC3S200-4TQ144C. The bold, underlined section represents the package designator. For Pb-free packages, an additional G is added to the package designator. For example: TQ144 standard would be TQG144 Pb-free.

Package Pin

Package pins are the physical pins of the package to which I/O ports are assigned. The package pins are grouped into I/O banks. Refer to the device specifications for more information about the package pins and I/O banks.

Packet

A unit of data transferred across a PCI EXPRESS link. The three types of packets are TLPs, DLLPs, and PLPs.

pad

The physical bonding pad on an integrated circuit. All signals on a chip must enter and leave by way of a pad. Pads are connected to package pins in order for signals to enter or leave an integrated circuit package.

pad-to-pad path P2P

A path which starts at an input of the chip and ends at an output of the chip. The pad-to-pad path time is the maximum time required for the data to enter the chip, travel through logic and routing, and leave the chip. It is not controlled or affected by any clock signal.

pad-to-setup path P2S

A path which starts at an input of the chip and ends at an input to a flip-flop, latch, or RAM--wherever there is a setup time against a control signal. The pad-to-setup path time is the maximum time required for the data to enter the chip, travel through logic and routing, and arrive at the output before the clock or control signal arrives.

PAL

See Programmable Array Logic.

PAO File

Peripheral Analyze Order file. The PAO file defines the ordered list of Hardware Description Language HDL files needed for synthesis and simulation.

PAR

Peak-to-Average Ratio.

See Place and Route.

parallel adder

An adder implementation in which the bits are added simultaneously. The carries of the parallel adders are connected, thus generating the sum simultaneously.

Parallel Cable III

A cable assembly which contains a buffer to protect the parallel port of your PC and a set of headers to connect to your target system.

PARTGen

A command which displays various levels of information about installed Xilinx devices and families depending on which options are selected.

partitioning

The process of splitting a single design among multiple devices.

The maximum level of integration density concern.

path

A connected series of nets and logic elements. A path has a start point and an end point that are different depending on the type of path.

path delay

The time it takes for a signal to propagate through a path.

PBCH

Physical Broadcast Channel

PBD File

Processor Block Diagram file

PCB

Printed Circuit Board

PCC

Predictive Command Controller

PCF files

Physical Constraints File. This file contains the physical constraints that are derived from the logical constraints after mapping. Any changes in constraints in the FPGA Editor are also written to the PCF.

PCFICH

Physical Control Format Indicator Channel

PCH

Paging Channel

PCI

Peripheral Component Interconnect

PCIBAR

Peripheral Component Interconnect Base Address Register

PCS

Physical Coding Sublayer

PDA

Parallel Distributed Arithmetic

PDCCH

Physical Downlink Control Channel

Portable Document Format

PDSCH

Physical Downlink Shared Channel

period

A clock period specification checks timing between all synchronous elements within the clock domain as defined in the destination element group. The group may contain paths that pass between clock domains if the clocks are defined as a function of one or the other.

The period specification is attached to the clock net.

PERR

Parity Error

PHICH

Physical HARQ Indicator Channel

PHY

Physical-side interface

PHYAD

Physical Address

Physical Block Pblock

A Pblock is defined in the PlanAhead software during floorplanning. Traditionally, a single or group of logic instances are assigned to a Pblock. The Pblock can have an area, such as a rectangle defined on the FPGA device, to constrain the logic. Netlist logic placed inside of Pblocks will receive AREA_GROUP constraints for the ISE software. Pblocks may be specified with specific RANGE types to contain various types of logic only such as SLICE, RAM/MULT, and DSP. Pblocks can be defined with multiple rectangles to enable non-rectangular shapes to be created, such as L shaped and T shaped.

physical constraints

Constraints that are attached to design elements in the physical design, that is, the design after mapping has been performed. These constraints are defined in the Physical Constraints File PCF, which is created during mapping.

Physical Layer

The lowest of the three layers in the PCI EXPRESS architecture.

PID

packet identifier field of USB packet

PIM

Physically Implemented Module. A term used in modular design that refers to the individual modules that have been completed and are ready to be incorporated into the top-level design.

pin

A symbol pin or a package pin. A package pin is a physical connector on an integrated circuit package that carries signals into and out of an integrated circuit. A symbol pin, also referred to as an instance pin, is the connection point of an instance to a net.

pin feedback

Pin feedback specifies that the associated signal comes from the actual device pin and not from the universal interconnect matrix UIM.

PIN2UCF

A Xilinx program that generates pin-locking constraints in a UCF file by reading a placed NCD file for FPGAs or GYD file for CPLDs. PIN2UCF writes its output to an existing UCF file. If there is no existing UCF file, PIN2UCF creates a new file.

PIP

See Programmable Interconnect Points.

PL

Programmable Logic in the Zynq-7000 All Programmable SoC. Equivalent to the FPGA in the 7 series devices

PLA

Programmable Logic Array

Place and Route

Place and Route PAR is a program for placing and routing an FPGA design. The process is called design implementation. Using back-end implementation software tools, Place and Route is the process of connecting various memory elements in an FPGA to create a custom logic circuit.

placer

A utility that maps logic from your design into specific locations in the target FPGA.

placer effort

The user-controlled parameter that balances run-time with placement efficiency.

placing

The process of assigning physical device cell locations to the logic in a design.

Platform

Xilinx defines platform as an umbrella term encompassing a set of technologies compiled and presented to customers as part of the design ecosystem. See also: Targeted Design Platform.

Platgen

Hardware Platform Generator sub-component of the Xilinx Platform Studio XPS technology.

PLB

Processor Local Bus

PLD

Programmable Logic Device. An integrated circuit composed of two types of gate arrays: the AND array and the OR array, thus providing for the sum of products algorithmic representations. PLDs include three distinct types of chips: PROMs, PALs, and PLAs. The most flexible device is the PLA in which both the AND and OR gate arrays are programmable. In the PROM device, only the OR gate array is programmable. In the PAL device, only the AND gate array is programmable. PLDs are programmed by blowing the fuses along the paths that must be disconnected.

FPGAs and CPLDs are classes of PLDs.

PLL

Phase-Locked Loop

PLP

Packet Layer Protocol

PLUSASM

A Xilinx proprietary Boolean equation language for expressing behavioral designs mapped to Xilinx CPLDs.

PMA

Physical Medium Attachment

PMCH

Physical Multicast Channel

PMD

Physical Medium Dependent

port

A logical connector that associates signals across hierarchical boundaries. Port location refers to a package pin on the IC.

POS-PHY4

Also, PL4. A 13.3 Gbit/second parallel link layer to physical layer interface for packet and cell transfer over SONET for OC-192c and 10 G bit/second Ethernet applications. POS-PHY4 is a 16-bit point-to-point interconnect with 832 Mb/sec per bit signaling utilizing double data rate clocking.

post-synthesis simulation

Simulation which is usually done after the HDL code has been expanded into gates. Post-synthesis simulation is similar to behavioral simulation since design behavior is being checked. The difference is that in post-synthesis simulation the synthesis tool s results are being checked. If post-synthesis and behavioral simulation match, the HDL synthesis tool has interpreted the HDL code correctly.

PRBS

Pseudo-Random Binary Sequence

PRCR

PCIe Requester Control Register

PRIDR

PCIe Requester ID Register

primitives

The simplest design elements in the Xilinx libraries. Primitives are the design element atoms, and can be combined to create macros. Examples of Xilinx primitives are the simple buffer, BUF, and the D flip-flop with clock enable and clear, FDCE.

probing

The process of examining the states of a device.

process

A running concurrent block of logic.The difference between hardware and software programming lies in the fact that hardware programming is for concurrent processes and software programming is for linear processes.

process technology

The procedure used to convert blank silicon wafers into finished wafers containing hundreds to thousands of chips. These chips are tested and assembled into plastic or ceramic packages before final use.

Product Mass

The product mass represents an average weight in grams. Package weights will vary slightly based on the die used in the package.

product of sums

The complement expression of a sum of products. Specifically, the outputs of a function for which the input combinations equal 0.

Product Term

The basic memory-based programmable logic element in CPLDs.

product term cascading

The process of passing groups of four product terms from one macrocell to another for the purpose of increasing the number of usable product terms.

Programmable Array Logic

A programmable logic device that consists of a programmable AND matrix whose outputs drive fixed OR gates. This was one of the earliest and, in terms of logic density, the simplest forms of programmable logic. PALs can implement small functions easily up to a hundred gates and run very fast, but they are inefficient for large functions.

Programmable Interconnect Points

The circuits that provide the routing paths used to connect the inputs and outputs of IOBs and CLBs into logic networks.

A PIP is made of a CMOS transistor, which you can turn on and off to activate the PIP.

programmer

A hardware box and its associated software that is used to program either the FPGA/CPLD devices themselves or the memory devices that are used to store programming data.

programming

The process of configuring the programmable interconnect in the FPGA.

Project Navigator

The main window for ISE. All of the GUI design tools for the ISE Design Suite are accessed through the Project Navigator software.

PROM

A programmable read-only memory.

PROM file

One or more BIT files bitstreams formed into one or more datastreams. The file is formatted in one of three industry-standard formats: Intel MCS86 HEX, Tektronics TEKHEX, or Motorola EXORmacs. The PROM file includes headers that specify the length of the bitstreams as well as all the framing and control information necessary to configure the FPGAs. It can be used to program one or more devices.

PROMGen

A Xilinx program that formats a BitGen-generated configuration bitstream BIT file into a PROM format file. The PROM file contains configuration data for the FPGA.

propagation

The transmission of signal from one point in a design to other points.

Constraint propagation refers to all of the design elements and nets that apply to a specified constraint in a design.

prototyping

The first full-scale functional model of a new device.

The use of a model prior to the generation of a final version of a chip.

PS

Processing System. The new processor portion of the Zynq-7000 All Programmable SoC.

PSC

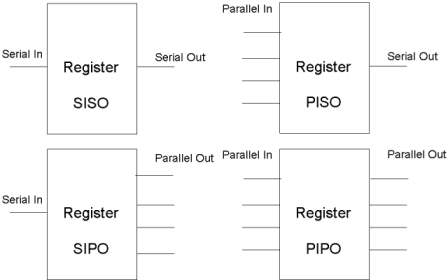

Parallel-to-Serial Shift Register

pseudo logic

Logic that is temporarily inserted in a design to facilitate the relative placement of the connected logic within a module. Pseudo logic is used when performing modular design.

PSF

Platform Specification Format. The specification for the set of data files that drive the Xilinx Embedded Development Kit EDK tools.

PSK

Phase Shift Keying

PSR

PCIe Status Register

PTM

Program Trace Macrocell debug/trace sub-module

PTP

Precise Timing Protocol

pull-down resistor

A device or circuit used to reduce the output impedance of a device, often a resistor network that holds a device or circuit output at or less than the zero input level of a subsequent digital device in a system.

pull-up resistor

A device or method used to keep the output voltage of a device at a high level, often a resistor network connected to a positive supply voltage.

PWM

Pulse Width Modulation

top.